# **PCT**

#### WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

## INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(51) International Patent Classification 4:

A1

(11) International Publication Number:

WO 89/12303

G11C 11/407, 11/406

(43) International Publication Date:

14 December 1989 (14.12.89)

(21) International Application Number:

PCT/GB89/00651

(22) International Filing Date:

12 June 1989 (12.06.89)

(30) Priority data:

8813795.5

10 June 1988 (10.06.88)

GB

(71) Applicant (for all designated States except US): CAM-BRIDGE COMPUTER LIMITED [GB/GB]; Bridge House, 10 Bridge Street, Cambridge CB2 1UE (GB).

(72) Inventors; and

(75) Inventors/Applicants (for US only): SINCLAIR, Clive, Miles [GB/GB]; WESTWOOD, James [GB/GB]; Cambridge Computer Limited, Bridge House, 10 Bridge Street, Cambridge CB2 1UE (GB). WRIGHT, David [GB/GB]; Cambridge Computer Limited, Bridge House, 10 Bridge Street, Cambridge CN2 1UE (GB).

(74) Agent: PEARS, David, Ashley; Reddie & Grose, 16 Theobalds Road, London WC1X 8PL (GB).

(81) Designated States: AT (European patent), BE (European patent), CH (European patent), DE (European patent), FR (European patent), GB (European patent), IT (European patent), JP, LU (European patent), NL (European patent), SE (European patent), US.

#### **Published**

With international search report

Before the expiration of the time limit for amending the claims and to be republished in the event of the receipt of amendments.

### (54) Title: MEMORY DEVICE

### (57) Abstract

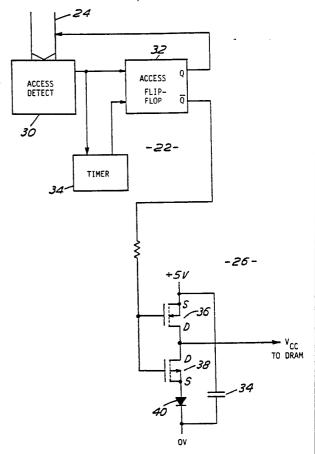

A dynamic RAM memory device with DRAM (10) comprises a control unit (22) detecting when memory accesses are required for read, write or refresh. This unit (22) controls a voltage control circuit (26) which provides operating voltage (e.g. +5v) to the DRAM (10) but switches the voltage to a low level (e.g. 0.5v) in intervals between accesses. The low level is such that the current taken by the DRAM (10) is substantially zero.